#### WYDZIAŁ INFORMATYKI

# Tomasz KRÓL

# PhD Thesis

Rozprawa doktorska

# Hybrid Optimization Algorithms applied to Model Reduction of EMI in GALS Systems

Wykorzystanie algorytmów optymalizacji hybrydowej do modelowania redukcji zjawisk interferencji elektromagnetycznej w układach GALS

## Supervisor:

PhD, Eng. Leonard Rozenberg, West Pomeranian University of Technology, Szczecin **Promotor:**

Dr hab. inż. Leonard Rozenberg, prof. Zachodniopomorski Uniwersytet Technologiczny w Szczecinie

Hybrid optimization algorithms applied

to model reduction of EMI in GALS systems

MSc, Eng. Tomasz Król

Supervisor: PhD, Eng. Leonard Rozenberg, prof. West Pomeranian University of Tech-

nology, Szczecin

**Abstract**

This dissertation investigates and presents the possibilities of reducing EMI in

GALS systems and its further automation by using a hybrid optimization. Several differ-

ent abstract models of GALS circuits have been designed in order to extract a realistic

pausable clock behavior. An advanced tool for analyzing EMI GalsEmilator has been

created in order to investigate the current profile of each modeled system according to

clock behavior. The research has been conducted both in frequency and time domain.

As a result, a reduction up to 26 dB can be achieved when applying a low-EMI GALS

methodology and the process of selecting GALS systems parameters can be automated

in order to achieve the best results.

Key words: GALS, EMI, current peaks, asynchronous design, hybrid optimization

1

#### DECLARATION

I hereby declare that I wrote the submitted PhD Thesis independently. During my work I have not, apart from necessary consultations, used any help from others; I have not instructed anyone to write or correct any of the following chapters. I have not copied any parts of the PhD Thesis from other authors. I also confirm that both paper and electronic copies of the submitted manuscript are identical. I understand that making a false declaration in this case will result in revocation of the decision to issue the diploma.

# **OŚWIADCZENIE**

Oświadczam niniejszym, że przedkładaną pracę doktorską napisałem samodzielnie. Oznacza to, że przy pisaniu pracy poza niezbędnymi konsultacjami, nie korzystałem z pomocy innych osób, a w szczególności nie zlecałem opracowania rozprawy lub jej części innym osobom, ani nie odpisywałem rozprawy lub jej części od innych osób. Potwierdzam też zgodność wersji papierowej i elektronicznej złożonej pracy. Mam świadomość, że poświadczenie nieprawdy będzie w tym przypadku skutkowało cofnięciem decyzji o wydaniu dyplomu.

# **Contents**

| Co | ontents                                         | 3    |

|----|-------------------------------------------------|------|

| 1. | Introduction                                    | 5    |

|    | 1.1. Theses and dissertation's objectives       | 6    |

| 2. | GALS Systems and EMI sense                      | 8    |

|    | 2.1. Introduction to current GALS methodology   | 8    |

|    | 2.1.1. Port Controller Types                    | . 12 |

|    | 2.1.2. Local Clock Generator                    | . 13 |

|    | 2.2. EMI in digital circuits                    | . 15 |

|    | 2.2.1. Modeling of current shape                | . 16 |

|    | 2.3. EMI reduction methods in digital circuits  | . 19 |

|    | 2.3.1. Passive EMI reduction methods            | . 20 |

|    | 2.3.2. Active EMI reduction methods             | . 21 |

|    | 2.3.3. Applied techniques                       | . 23 |

|    | 2.3.4. Jitter generator                         | . 24 |

|    | 2.4. GALS practical example in reducing EMI     | . 31 |

| 3. | Modeling EMI in digital systems                 | . 40 |

|    | 3.1. GALS EMI simulator                         | . 40 |

|    | 3.1.1. Simulator description                    | . 41 |

|    | 3.2. Hybrid optimization algorithm              | . 46 |

|    | 3.3. GALS modeling                              | . 49 |

|    | 3.3.1. Topologies of the evaluated GALS systems | . 50 |

|    | 3.3.2 Data transfer scenarios                   | . 51 |

|    | 3.3.3 Model parameters                          | . 52 |

| 4. | Investigations and experimental results         | . 57 |

|    | 4.1. Synchronous systems                        | . 57 |

|    | 4.2. Evaluating GALS systems                    | . 62 |

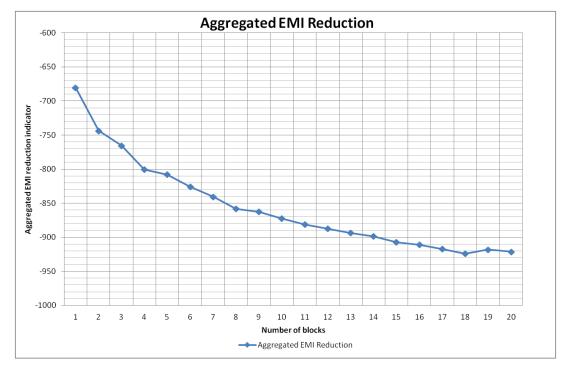

| 4.2.1. GALS granularity vs EMI reduction limits             | 69  |

|-------------------------------------------------------------|-----|

| 4.3. Evaluation of solutions using jitter                   | 76  |

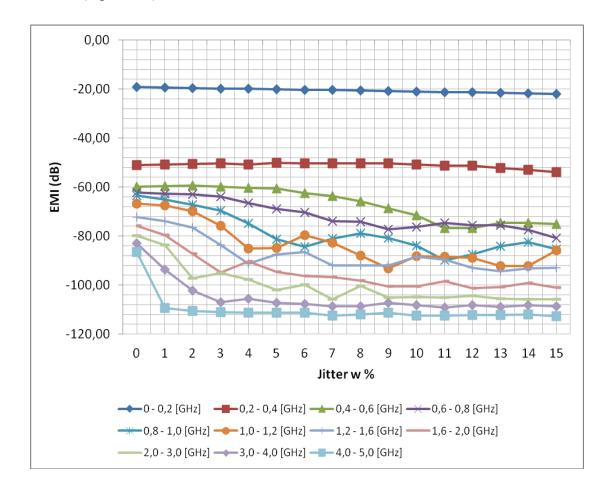

| 4.3.1. 10 modules synchronous system                        | 77  |

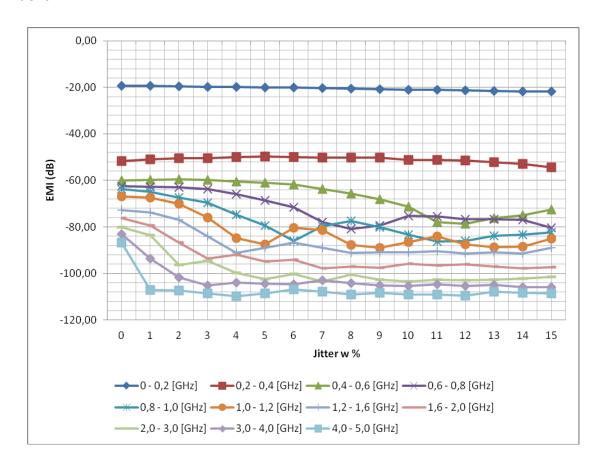

| 4.3.2. 4 modules synchronous system                         | 78  |

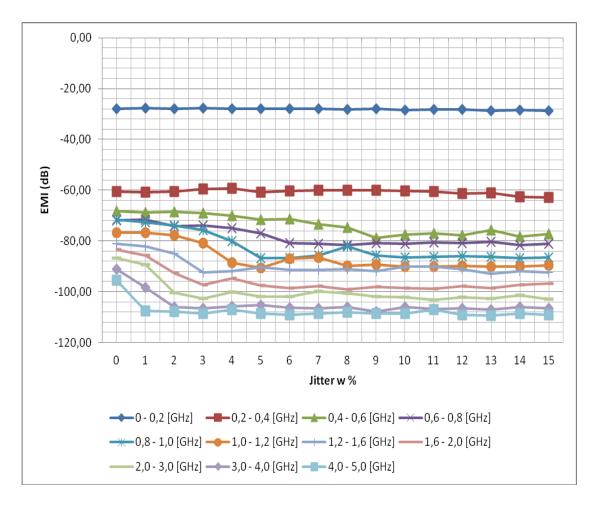

| 4.3.3. 4 modules GALS system                                | 79  |

| 4.4. Comparison synchronous with GALS systems               | 80  |

| 4.5. Hybrid optimization results                            | 84  |

| 4.5.1. 4 blocks GALS system with different initial settings | 84  |

| 5. Summary                                                  | 91  |

| References                                                  | 95  |

| List of Figures                                             | 102 |

| List of Tables                                              | 106 |

| Appendix A. DVD Contents                                    | 109 |

| Streszczenie w języku polskim                               | 110 |

| Acknowledgements                                            | 113 |

# 1. Introduction

From the time when the first silicon chip was invented, there has been a continuous improvement and miniaturization of that technology. In recent years the manufacturing process has become more and more advanced leading to miniaturization of the systems which proves challenging for the system designers. The basic synchronous approach in chip design became more challenging because of problems with its dimensions. It turned out that the most problematic is the size of a clock tree and fulfilling proper timing constraints. Moreover, because of the miniaturization the chips are more prone to a noise generated by digital components. Hence, a new methodology had to be applied to decrease the level of EMI (Electromagnetic Interference). The GALS (Globally Asynchronous Locally Synchronous) approach has been presented as a solution for the system design many years ago [7], [49]. It has also been proposed to utilize GALS systems for EMI (Electro-Magnetic Interference) lowering in digital circuits [1]. Several examples have shown that asynchronous design can significantly reduce EMI in comparison to the classic synchronous design, one being - an asynchronous design of an ARM9 processor - Amulet 2 [2]. Some initial studies regarding the GALS approach for EMI reduction have been conducted [1]. Those have shown that the GALS systems can achieve EMI reduction of up to 20 dB in comparison with a synchronous design. In time domain, the noise peaks can be lowered up to 40%. Initial studies and real on-chip measurements [3], [4] have shown about 5 dB smaller reduction of EMI. However, further investigation proved the possibility of EMI reduction at the level of 26 dB [26], [3].

Moreover, those activities were not systematic and were focusing only on specific design cases, not taking into consideration GALS as a general methodology for system integration. The technology advance and further device miniaturization increases a demand for deep investigation of EMI because of its detrimental influence on a whole system performance.

Initial studies have been completed to use FPGA (Field Programmable Gate Area) technology as a testing platform for GALS systems [28], [29]. However, it transpired that FPGA has a lot of drawbacks regarding GALS implementation [29], mainly because of poor clocking systems in FPGA chips [30] and complicated routing schema. Thus fur-

ther exploration of FPGA as a testing platform has been dropped and focus is now on ASIC technology.

Moreover, there are no dedicated tools to model EMI in GALS and synchronous circuits on a high abstraction level. It is needed to have the possibility to predict at least approximate values of EMI in designed digital systems. In synchronous systems, which are much more evaluated because of their wide application, it is easier to estimate EMI. There are many investigations showing the possibility of reduction of EMI in synchronous systems by adding clock skew and phase modulation of the clock [33], [6]. However, adding a clock skew or a phase modulation of a clock to a synchronous chip demands additional work and sometimes generates very difficult problems in timing closure.

# 1.1. Theses and dissertation's objectives

The theses of this work were formulated as follows:

In this dissertation it is assumed that it is possible to set such parameters of GALS digital systems that the EMI generated by these systems is evidently lower than in synchronous digital systems without applied features to reduce EMI. Moreover, the process of selecting parameters of GALS system can be automated by using hybrid optimization algorithm. The final result should be a set of reasonable parameters of GALS system that generate EMI evidently lower comparing to its initial state.

In order to prove such a thesis partial aims are defined as follows:

- present GALS system architectures impact examination for possible EMI reduction,

- proposition of an optimizing hybrid method used to reasonable selection of GALS system power control parameters to reduce EMI at the stage of digital system design.

It means, that the aim of this work is facilitating cross-benchmarking of EMI features for GALS and synchronous design style. It is important to make such EMI analysis, which would let system designers choose solutions optimal for their needs. The first step to prepare this is to create software able to model and evaluate EMI in synchronous and GALS systems. In my dissertation, I would like to present a software tool able to simulate the EMI behavior caused by clock activity in GALS and synchronous systems on a very high abstract level. This tool is able to model additional features such as introduced jitter, pausable clock, phase shift that can be embedded into GALS or synchronous systems in order to reduce EMI characteristic.

This tool enables performing many simulations in order to investigate the best way to reduce EMI in GALS and synchronous circuits. Several GALS topologies have been evaluated and compared to their synchronous counterparts.

However, performing manually thousands of simulations is not an efficient way to obtain fair results. Thus, a hybrid optimization algorithm has been proposed to automate the process in order to facilitate circuit designers' decisions. It allows setting ranges of parameters e.g. frequencies of each GALS block and running hundreds of simulations in order to obtain the best results regarding EMI reduction in GALS systems. Such a technology moves us a step forward in the design of electronic GALS circuits in the matter of reducing EMI.

The dissertation is structured in a following way: Chapter 2 describes GALS methodology, its structure, components and behavior. Additionally, EMI in digital circuits, its sources and the possibilities of its reduction are presented. This chapter also includes a case study. In Chapter 3, the accurate (not only mathematical) models of GALS systems are discussed, and the software used to model EMI is presented. Moreover, a hybrid optimization algorithm, applied in further investigations, is described. In Chapter 4, the results of simulations for different GALS topologies, different granularities of digital systems, various EMI reduction methods applied, are presented and compared with synchronous designs. Furthermore, results of hybrid optimization algorithm are shown. In final section conclusions are drawn from the data presented throughout the paper.

# 2. GALS Systems and EMI sense

In this chapter the issues of GALS systems and EMI in digital circuits are explained [20]. First, the GALS methodology is described. The instances of GALS interfaces are demonstrated. In particular, port controllers and local clock generators are presented. In addition, modeling of current shapes is explained regarding EMI in digital circuits. The possibilities and methods of EMI reduction in digital circuits are described: especially, clock generator modifications are pointed out. For instance, clock skew and phase modulation applicable to digital circuits are presented. In the chapters' conclusion a case study is demonstrated.

# 2.1. Introduction to current GALS methodology

**GALS** is quite an original technology for VLSI class circuits designing, it is not well defined yet [35], [63]. GALS systems are a compromise linking totally synchronous design and the asynchronous one [39], [50]. Therefore GALS builds on the advantages of both systems [52]:

- GALS are easy to integrate, because of an asynchronous communication any

existing synchronous chip can be utilized and combined with any other without concerning the frequency at which they are supposed to work.

- GALS are useful for existing synchronous solutions regarding its structure; it is

possible to use any synchronous design and with only minor changes adopt it

to work as a Locally Synchronous (LS) island in GALS systems [44].

However, GALS is not only a class of circuits, but also a methodology that is still not well defined and investigated [62] e.g. in the field of EMI and subsequently it is not widely used. The potential is known but the lack of predefined libraries and standards does not encourage commercial companies to use it as a possible solution for market products.

It is generally stated, that GALS consists of combining multiple synchronous blocks through an asynchronous communication [38], [47], [54]. It does not define any

specific way in which the communication should be driven by two adjacent blocks. For that reason several solutions, presented in subject literature, can be found:

- S. Smith [13] presents a GALS system without pausable clocks. Instead, synchronizers are used to avoid metastability. Also Chattopadhyay [14] describes similar design where bidirectional asynchronous FIFO [48], [61] components are used to avoid metastability.

- A specific approach has been presented for data path architectures. A communication circuit presented by M. Krštić [3] is able to process big data frames as a batch. After a burst data transfer a period of inactivity occurs. The local clock is obtained through a specific handshake. Therefore, there is no necessity to use any additional clock generator. A similar approach has been also proposed by J. Kessels [15].

- S. Moore et al. [16] proposed GALS system utilizing a 2-phase bundled data communication approach. A ring oscillator [60] acting as a pausable clock generator was used to prevent metastability during data synchronization between two adjacent modules. Another version of that approach has been presented in [42].

- D. Bormann [17] presents a GALS system utilizing as a 4-phase bundled asynchronous data communication. Pausable local clock generators [34] are used in order to prevent metastability during a handshake between adjacent blocks [45], [47], [46]. J. Muttersbach [7] describes a similar approach in his thesis. He defines precisely the structure of GALS systems with different port types.

For the purpose of this PhD Thesis, methodology described by J. Muttersbach [7] will be used when discussing GALS.

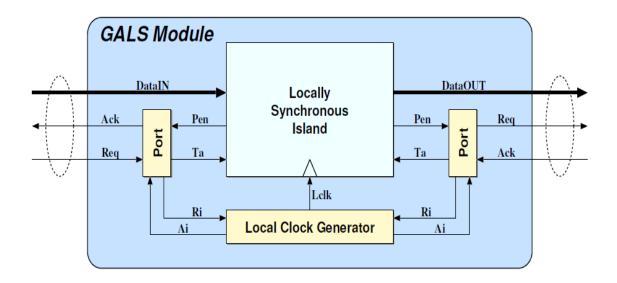

In Figure 2.1 a basic block of a GALS system is illustrated. At the center of each block a *Locally Synchronous* (LS) Island is placed. It is designed by standard tools dedicated for typical synchronous systems. The LS Island contains the functionality of the whole block. Additionally, the Island is surrounded by a GALS wrapper. The wrapper contains input and output ports controllers, data paths and local clock generators. The local clock generator delivers a clock signal for an LS Island.

Figure 2.1. An overview of a single GALS module with an input and an output port [18]

Port controllers are used to drive a handshake between adjacent blocks before the data transfer occurs. They are the asynchronous finite state machines (AFSM). In order to prevent metastability and provide a successful handshake, port controllers can stop a local clock generator.

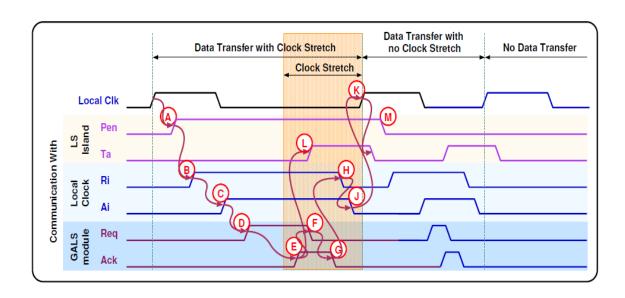

Figure 2.2 presents a timing plot with three successive clock cycles of a D-type output port controller. The port controller is described in details in the next subchapter. In the chart, the GALS block utilizes a four-phase bundled handshake protocol in order to transfer data to a similar GALS block. The most important signals that drive the whole procedure are illustrated and divided into three groups:

- LS Island signals: *Pen* (Port Enable), *Ta* (Transfer Acknowledge from port controller)

- Local Clock signals: Ri (Request to a local clock), Ai (Acknowledge from a local clock)

- GALS module signals: Req (Request to an adjacent GALS module), Ack

(Acknowledge from an adjacent GALS module)

Figure 2.2. Timing for a D-type output controller for three consecutive clock cycles;

In the first cycle shown, the environment is slow to react to the Req signal.

As a result the clock is stretched until the data transfer has been processed.

The second cycle shows another transfer where the handshake finishes within the clock cycle. Finally in the third cycle, the Pen signal is not enabled, and no data transfer is initiated [18]

Moreover, in Figure 2.2 a Local Clock (*Clk*) signal is presented. Port Enable is utilized by the LS Island in order to trigger the port controller (A). Next, the port controller instantly sends a request signal (*Ri*) to stop the local clock generator (B). When occurrence of a new active edge of the clock signal is prevented, the local clock generator changes a state of the acknowledge signal (*Ai*) to a high-state (logic-1). From that point, no new rising edge of a clock will be generated. The activity of an LS island is stopped. Subsequently, the *Req* signal is activated (D) by the port controller. It informs the receiving GALS module that a new part of data is ready to be transferred. When the receiving GALS module is prepared to accept data, its port controller undertakes the similar steps. It raises the *Ack* signal to the high-state in order to confirm receiving of the *Req* signal from the transferring GALS module (E). As soon as both the GALS modules are paused, the receiving one can safely accept the data. When the transfer is established, the handshakes signals go back to their initial states. The local clocks generators are released and a new clock signals can occur. *Req* is deactivated first at the transmitting side (F). When *Ack* signal is deactivated by next module, the local clock generator

is activated by releasing the *Ri* signal (H). Next, the local clock generator sets *Ai* signal to low-state and starts to generate clock pulses (K). Finally, the port controller informs the LS island about a successfully completed data transfer by setting a transfer acknowledge (*Ta*) signal (L) to a high-state [18].

During the handshake procedure presented above, it can be noticed that the LS Island initiate a data transfer by changing the state of the *Pen* signal. In the first cycle, the handshake is triggered by a rising edge of the *Pen* signal. In the second one, communication is triggered by a falling edge of the *Pen* signal. In the third cycle, no change of the *Pen* signal occurs. Thus, the handshake procedure in that system is triggered by transition of the *Pen* signal. Falling or raising edge of a signal do not affect the outcome. Hence, the data transfer in two phase protocol is doubled in comparison to a standard four phase protocol. This feature is applied only to the *Pen* signal.

During the first cycle in Figure 2.2 the stretched clock can be observed. This situation is caused by the sending block that awaits the Ack signal from the receiving one. It slows down slightly the LS block functionality. However, it ensures that an adjacent block is ready to receive data. That pause of the clock will be analyzed later because it adds a natural phase shift to the GALS system. Pausable clock in several GALS blocks can generate a total disharmony. Even if the frequency of each GALS block would be the same, the pausable clock is able to mix their phases. Hence, pausable clocking can influence EMI in GALS systems.

#### 2.1.1. Port Controller Types

In Figure 2.2 the clock generator is stopped directly after the LS Island is ready for data transferring. This situation is necessary in a system, which cannot continue to operate normally without finishing the current data transfer. According to Muttersbach [7], [8] there are two types of port controllers:

- 1) 'Demand Type' (D-type) ports stop the clock generator directly after they are requested to introduce handshake procedure. These are presented in Figure 2.2 and described above.

- 2) 'Poll Type' (P-type) ports in contrast to the D-type controllers, P-type controller does not stop local clock generator as soon as the Pen signal changes its state. It allows the LS island to continue its normal work until a data dependen-

cy appears. First, when the *Pen* signal transition occurs, the port controller sends a request to an adjacent block. It does not stop a local clock generator until the acknowledge signal (*Ack*) comes from an adjacent block. When a rising edge of the *Ack* signal occurs, port controller immediately generates a high state of the *Ri* signal in order to stop a local clock generator. Then a typical fourphase handshake follows. When the data transfer is established, all signal values return to their initial states.

#### 2.1.2. Local Clock Generator

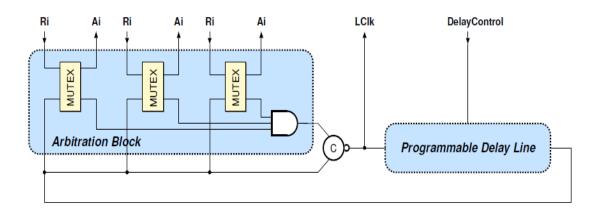

**Figure 2.3.** Simplified block diagram of a pausable local clock generator [18]

In order to prevent metastability in GALS systems during data transfer, Pausable Local Clock Generator has been introduced to the system by Muttersbach [7]. Hence, port controller can easily operate having an ability to stop the LS island when it is necessary and successfully complete the data transfer between the adjacent GALS blocks. In Figure 2.3, created by Gurkanyak [18], a simplified block diagram of a pausable local clock generator is presented. It is generally a ring oscillator with a Programmable Delay Line. The Delay Line is used to set the period of the clock. An Arbitration Block allows each port controller to pause a clock in order to conduct a handshake protocol without introducing metastability to a system.

The usage of a ring oscillator as a Local Clock Generator is a very rational approach to EMI reduction. It allows each GALS block to work with its own frequency and phase [36]. Thus, the frequency spectrum of a whole chip is spread and lowered.

The Local Clock Generator contains several input and output ports accordingly to the number of port controllers in a GALS wrapper. Each of the port controllers has

the ability to pause the clock generator by applying the high-state to the request signal (*Ri*). The signals connected to the port controller are joined with an output of Programmable Delay Line through a <u>Mut</u>ual <u>Ex</u>clusion Component (MutEx). MutEx is a specific element that propagates only one high state signal during a fixed time. For that reason, when a request to pause the clock has been introduced, no positive clock edge would appear. Several implementations of the MutEx have been presented in the literature i.e. [18]; those will not be discussed in detail as they fall outside the scope of this thesis.

There is only one possible state of all the *Ri* signals when the local clock can be propagated through the arbitration block. The *Ri* signals must be in the low-state in order to avoid blocking of a rising clock edge by *MutEx* element. The Arbitration Block is further connected with a Muller-C component that changes its state only in case when both the signals have the same state. The local clock generator will be paused as long as one of the *Ri* signals remains in high state (logic-1). The MutEx informs the port controller if the pausing of local clock generator was successful achieved by changing acknowledge signal (*Ai*) to high-state (logic-1). As long as *Ai* is at high-state the clock will be paused. When the port controller lowers *Ri*, after a while *Ai* is also lowered and a new rising edge of the clock generator can occur.

The local clock generator is mainly interesting because of its ability to set defined frequency of a clock by adjusting a programmable delay in line. This in turn facilitates programming different GALS system by changing only one value per GALS module. In several GALS topologies that are described later, this advantage of GALS system has been employed. It speeded up modeling of GALS systems with different sets of frequencies.

Although, the maximum number of ports of a pausable clock generator is not defined, connecting the outputs from too many ports controllers decreases the highest achievable clock frequency. In practice, local clock generators with up to 8 ports have been designed and investigated [18].

Recently a new approach for Pausable Local Clock Generator has been proposed by E. Grass et al. [1]. Instead of an internal local clock generator (presented before), a new externally clocked wrapper has been proposed. It delivers a clock to different GALS blocks with the same frequency but with a different phase. However, it is not a desired

solution for GALS systems where the most important issue is an EMI reduction. The main drawback of this solution is the same frequency for the whole digital circuit.

## 2.2. EMI in digital circuits

An EMI phenomenon in digital systems is caused generally by the simultaneous switching of logic components [33]. Each active edge of a clock pulse, in a synchronous system, triggers all flip-flops that generate noise. This triggering is not exactly at the same moment because of the clock tree and its skew that spreads triggering of the flip-flops in time [55]. The easiest way to analyze EMI generated by the digital circuits is to evaluate the sources' current shape. Reduction of EMI is possible in several ways including improvement of physical elements. However, I have focused in my thesis only on the modification of a clock behavior by adding a jitter or a fixed phase to each sub block.

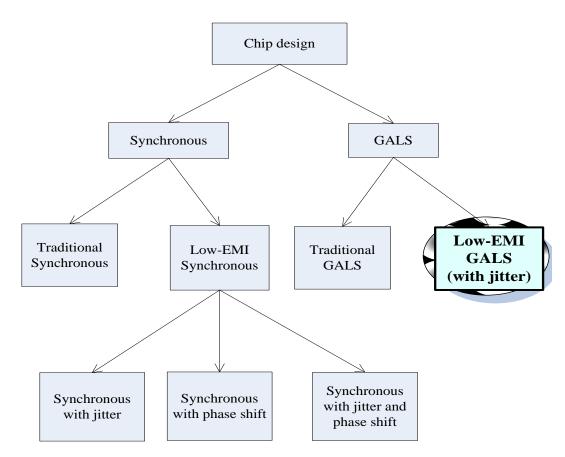

**Figure 2.4.** Chip design styles concerning EMI reduction, where Low-EMI GALS systems are the object of this dissertation

In Figure 2.4 various chip design techniques concerning EMI reduction have been presented. First circuits can be divided into GALS and Synchronous systems. GALS systems are understood as a number of sub blocks that can operate with different frequencies and with pausable clocks. Thus, applying a phase shift to a GALS sub block would have no impact on EMI reduction. Phase shifting is in nature of GALS systems. For that reason, GALS chips are divided into the traditional ones and Low-EMI GALS with jitter applied. On the other hand, the synchronous systems can be divided into the traditional ones and Low-EMI. A traditional synchronous system represents a circuit with one clock domain. The clock tree is usually so spacious that a natural clock skew occurs. Low-EMI synchronous systems are further divided into three categories according to incorporated features. Therefore, a synchronous system can contain:

- Jitter

- Phase shift

- Jitter + phase shift

#### 2.2.1. Modeling of current shape

In order to construct a more realistic model of EMI of any digital system, an accurate current shape profile is required. The current shape profile describes the power consumption of a circuit in a time domain according to its activity during a clock cycle [32], [52]. Having the power consumption of a system in a time-domain [5] it is possible to estimate EMI, which is directly caused by the activity of the circuit.

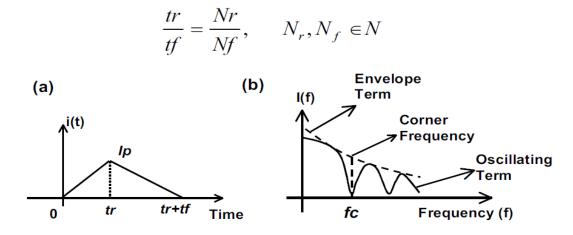

**Figure 2.5.** Triangular approximation of the supply current in (a) time-domain and (b) frequency domain [10]

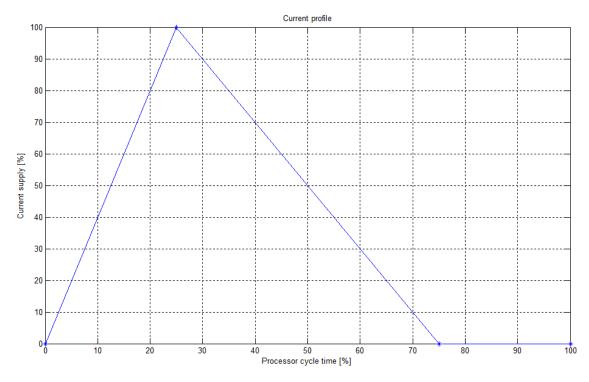

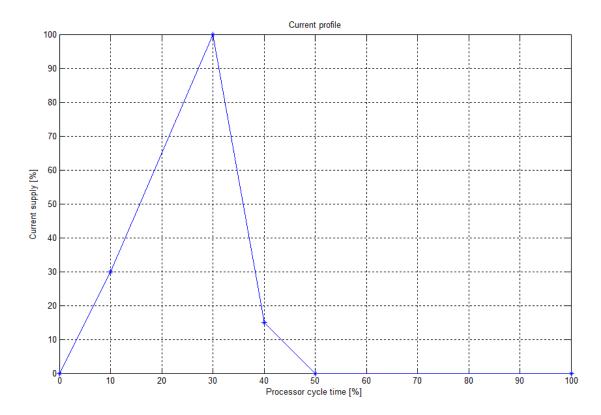

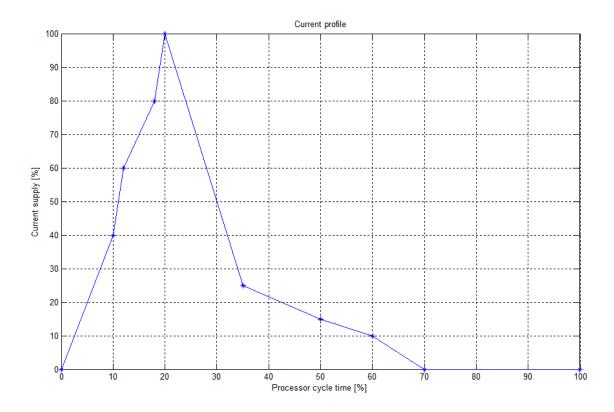

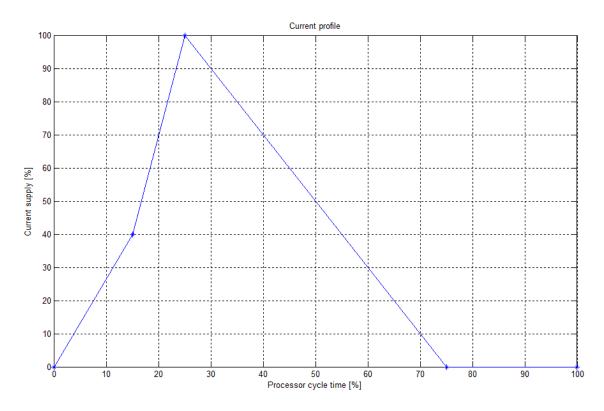

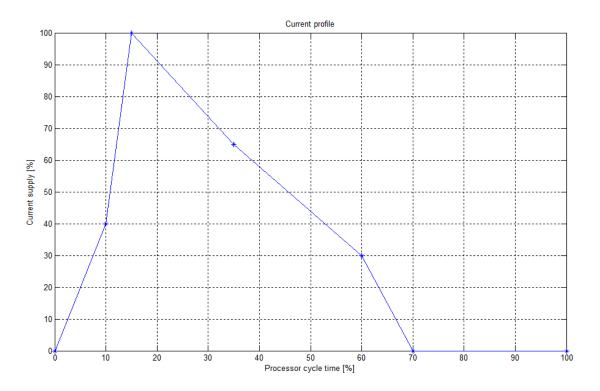

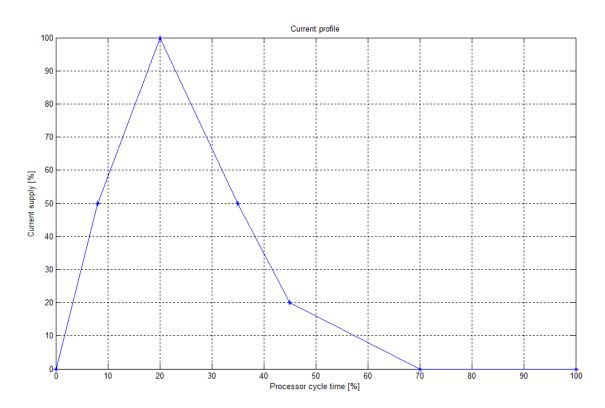

However, it is very difficult to define the current shape for each digital block and in each clock cycle, when the system is defined on a very abstract HDL level. The current profile varies significantly in each design. Additionally, it can change from cycle to cycle depending on activity and processing load [41]. For that reason, one of the most challenging tasks is to model a current profile in each clock cycle. In [33], [10] it is presented that for digital circuits triangular modeling of the current shape can be sufficient. In Figure 2.5 triangular supply current is presented both in time-domain and frequency-domain. The *Ip* point is a current peak, *tr* is a increase time, *tf* is a decrease time. It is said that generally *tr* takes 25% of processor cycle, *tf* takes 50% of processor cycle and 25% is necessary for stabilization of all signals and responsible for that action flip-flops. This scheme is presented in Figure 2.6.

Figure 2.6. Sample model of a current profile of a processor cycle

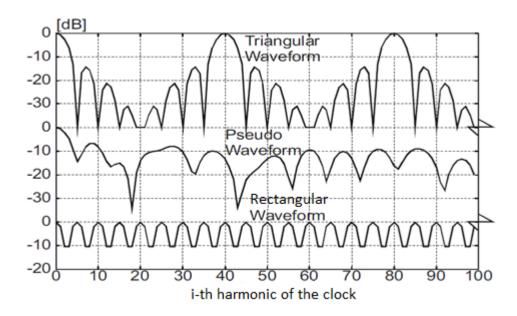

Moreover, in Figure 2.7 frequency spectrum of different current waveforms is presented. It can be observed that a reduction of amplitude in frequency domain can be achieved by applying different shapes of waveforms. The lowest values are presented with square waveform, whereas the highest with triangular and pseudo random waveforms. Thus, the more flat current shape, the lower values in the frequency domain.

**Figure 2.7.** Frequency spectrum of the different modulating waveforms: Triangular, Pseudo Random and Rectangular [10]

However, the results presented above are too general. Depending on the logic activity in the chip there can be totally different current shapes for each clock cycle. For instance, the triangular model cannot always emulate real behavior of the digital circuit. The current profile could be modeled as a superposition of two or more triangular shapes for some elaborated systems [11].

To support this assumption a realistic digital synchronous circuit has been modeled. It was composed of:

- Complex sequential stage (512 flip-flops)

- Combinational logic (813 basic combinational cells)

- Reset

- Clock tree (369 buffers)

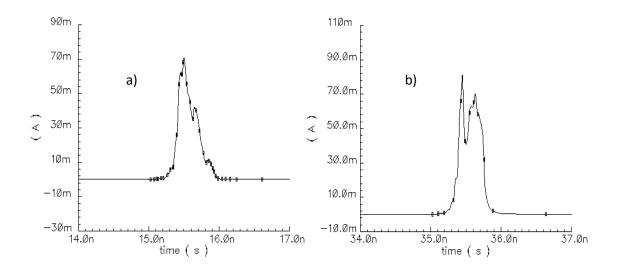

The circuit has been modeled by Miloš Krstić in 0,25 µm CMOS technology from IHP (Institute for High Performance, Frankfurt (O), Germany) and simulation was completed in different scenarios in Cadence Spectre [11]. Two examples are shown in Figure 2.8. The current shape from 1a) can be modeled as a triangular shape, however, for 1b) a more precise model would be the superposition of two triangles.

Figure 2.8. Analog current profile simulation using 0.25 um CMOS process [11]

# 2.3. EMI reduction methods in digital circuits

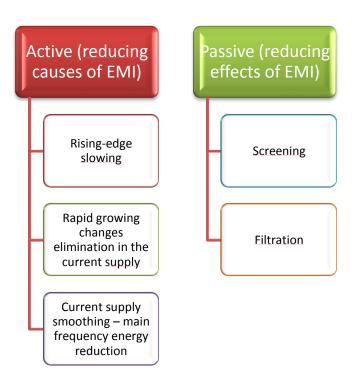

Generally, there are two categories of methods that are able to reduce EMI in digital circuits (Figure 2.9) [10]. First one is classified as passive methods, based on adding a special material to a digital circuit (usually on PCB) in order to diminish EMI effect. Passive methods impact only the effects of EMI occurrence. The second category is known as active methods which impact causes of EMI.

Figure 2.9. General methods of reducing EMI in digital circuits

#### 2.3.1. Passive EMI reduction methods

There are two main passive methods: screening and filtration [51]. Screening is a mechanical solution, depending on adding special fabrics to a digital circuit in order to prevent spreading of EMI among different parts of digital circuit e.g. paths, input/output signals, signals with different characteristics, parts of PCB or even blocks of processors. Filtration on the other hand, depends on filtering unwilling range of frequencies that can occur because of electromagnetic interference in a circuit. Set of rules for digital circuit designers regarding passive methods application can be found in literature [21]:

- connect unused recurring operational amplifiers inputs to ground, and connect the inverted inputs with outputs,

- filter signals from noisy sources,

- filter all signals connected to PCB/processor,

- place buffers and I/O controllers directly by the I/O connectors on the edges of the PCB,

- place clock generator in the middle of the PCB,

- separate the sub-systems according to their operating frequencies and level of signals,

- provide separation/screening between signals with high noise and low noise,

- provide separation/screening between digital and analog signals and place them away from each other,

- place clock signals paths and digital signals paths away from analog inputs and reference voltage inputs,

- place clocking systems away from the I/O connections,

- minimize the length of critical paths (blocking capacitors should be placed as close as possible to the IC),

- use all power terminals,

- use a twisted-pair cable to minimize feedback, if it is possible,

- use additional ground connections to reduce the coupling between signals in connectors,

- use short and simple lines with RF signals,

- avoid placing paths under quartz generators,

- avoid carrying sensitive signals in parallel to the fast-changing signals,

- use wide paths for critical signals and provide parallel ground paths on both sides.

#### 2.3.2. Active EMI reduction methods

Active methods are used to prevent occurring or to reduce the occurrence of EMI in digital circuit. They impact the causes of EMI. First of all, the EMI can be reduced as a result of a slowing signals' rising edge. The power of main harmonics is dissipated in a wider frequency range. However, it is a risky method where glitches can appear (can generate additional transients) and signal/system noise to power ratio is reduced. Thus, that method is not recommended in most practical digital solutions.

The most popular method is eliminating rapid changes in current supply. It can be archived, for instance, by spread clocking (forced spread over time of rising edge supplying individual components in digital electronic circuit) [58]. This method consists of spreading the clocking signal into a wider range of time among the processor. It is a common technology used in most computers nowadays because it doesn't require any additional processor components to achieve good results. It requires only special design of an integrated circuit where clocking signal paths are placed according to the delay they generate. Thus the <u>Simultaneous Switching Noises</u> (SSN) [57] are spread over time between different parts of the processor. However, this technique also requires designers to take care of timing constrains which are the most significant to keep the proper working of flip-flops, its set-up time, of whole integrated circuit. This technique is applicable mainly in synchronous designs with one clock domain.

Finally, current supply smoothing methods can be utilized to reduce EMI in digital circuits. It is similar to rapid current supply changes elimination but puts more effort on smoothing the whole current supply wave. First of all, a **S**pread **S**pectrum **C**locking (SSC) [56] can be utilized. It depends on spreading the clocking signal into a wider range of frequencies and it is called jitter. SSC depends on changing the clocking frequency according to a special pattern. It can be either a pseudo-randomized selecting solution or a deterministic one, for instance triangular selection, where a modulating signal has a triangular shape. This technique can be used both in synchronous or asynchronous designs. The next method of smoothing supply current signal is applicable only in asynchronous designs, such as GALS systems, where different sub-blocks work with different frequencies and continuous phase shift of clock signals among sub-blocks.

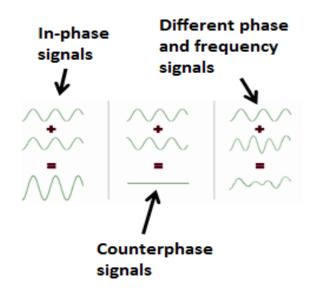

Figure 2.10. Sample mutual influences of two electric signals

As it is presented in Figure 2.10, when two similar signals are in-phase then their amplitudes are added and create signal with a double power. It can be assumed that a synchronous processor is combined with a number of such in-phase signals, thus generates strong current peaks and high EMI. On the other hand, there are two out-of-phase signals which generate a constant waveform with only one peak in a frequency domain. It is an ideal solution with constant current supply requirements. However, achieving such a waveform is almost impossible in real life where processor contains

thousands of flip-flops. But it is possible to get close to those results by shifting a clock signal in phase among different parts of processor. Traditional synchronous design could not stand such a solution because of restrictions in timing-constraints. GALS technology is able to do that and also provide a possibility to apply different frequencies to each sub-bloc. This solution deepens a smoothing of current supply waveform.

#### 2.3.3. Applied techniques

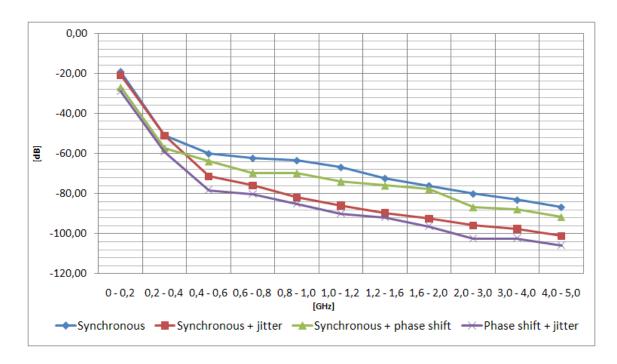

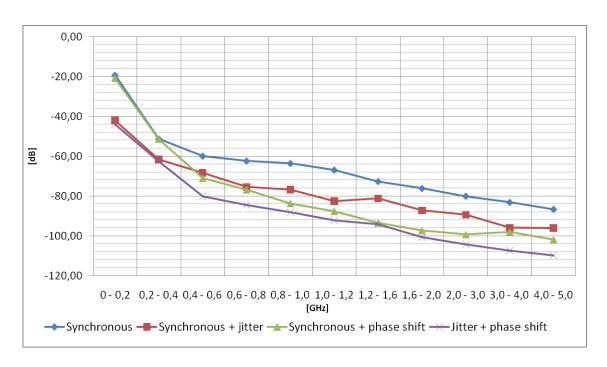

It is said that two main techniques are used to reduce EMI in synchronous systems by modifying clock behavior [1]. First a clock phase shift can be added to each LS block. Phase shift decreases the current peaks for a whole circuit, thus reducing EMI. Additionally, jitter can be added to the clock source [10], [19].

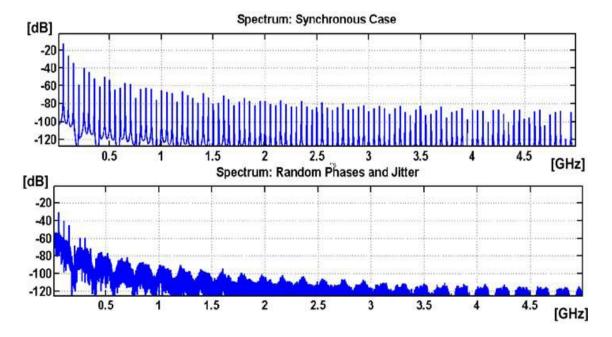

**Figure 2.11.** Power spectrum of supply current for synchronous circuit (top) and its equivalent GALS implementation (bottom) [1]

The results of combining both of those features in a GALS system in comparison with a synchronous approach has been presented in Figure 2.11 [1]. It is clear that EMI can be reduced up to 15 dB. However, the GALS system utilized in that model was firmly simplified with respect to the full potential of GALS systems. It was assumed that all 10 sub blocks operate with the same frequency (50 MHz). Thus, it resembles more a synchronous approach than a GALS system. The possibility of different clock generators (different frequencies) for each sub block regarding EMI reduction was also not investi-

gated. Moreover, applying a phase shift to each sub block indicates that GALS pausable clock was not analyzed too. Therefore, it is safe to conclude that more detailed investigation is required to fully analyze the possibility of EMI reduction in GALS systems.

#### 2.3.4. Jitter generator

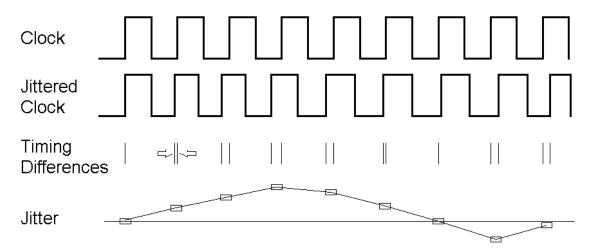

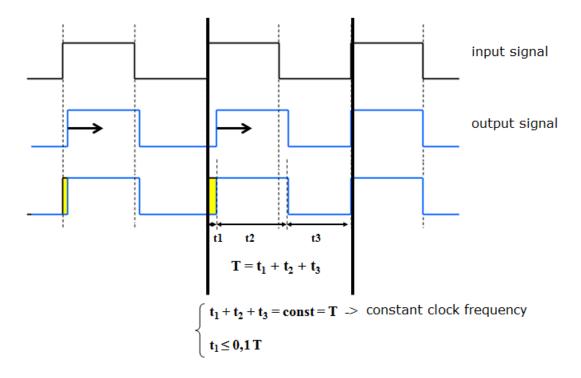

Jitter (Figure 2.12) introduces a phase modulation (most often random rapid phase fluctuations) to a clock wave from cycle to cycle (Figure 2.13). It influences EMR (Electromagnetic Radiation) [10]. Jitter modifies slightly, up to a defined part of a period, the starting point of a rising edge, while the time of the high level stays constant [31], [59]. Hence, jitter can increase or decrease the clock period for a cycle but the average base frequency remains the same. The change can be generated either randomly or deterministically.

Figure 2.12. Jitter; phase variations between two signals [24]

Figure 2.13. Jitter generator functioning schema

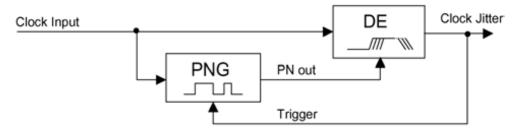

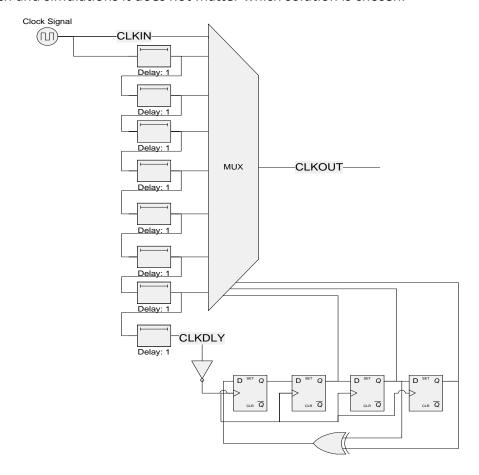

In Figure 2.14 the principal structure of a jitter generator is presented. Similar approach has been described in a U.S Patent [12]. However, neither of those works presents a solution that can be directly described in a VHDL code due to lack of analysis in that direction.

**Figure 2.14.** Principal structure of a jitter generator [1]

Generally, jitter consists of Pseudo Noise Generator (PNG) and Delay Element (DE). Pseudo noise generator is responsible for selecting relatively randomly a delay. The delays are created by a Delay Element that consists of propagating variously belated signal. However, triggering a Pseudo Noise Generator by an output clock of jitter generator is risky. The glitches can occur between two different cycles due to the lack of proper setup time of the Pseudo Noise Generator. A better way to handle this depends on adding an extra delay to the Delay Element. That delay would last longer than

a maximal possible jitter size. Thus, the Pseudo Noise Generator would have enough time to set properly its outputs before the next cycle of the clock input occurs. This approach is presented in details in Figure 2.17.

Table 2.1. First 19 polynomials of LFSRs

| Bits | Feedback polynomial                     | Period             |

|------|-----------------------------------------|--------------------|

| n    |                                         | 2 <sup>n</sup> - 1 |

| 4    | $x^4 + x^3 + 1$                         | 15                 |

| 5    | $x^{5} + x^{3} + 1$                     | 31                 |

| 6    | $x^{6} + x^{5} + 1$                     | 63                 |

| 7    | $x^{7} + x^{6} + 1$                     | 127                |

| 8    | $x^{8} + x^{6} + x^{5} + x^{4} + 1$     | 255                |

| 9    | $x^9 + x^5 + 1$                         | 511                |

| 10   | $x^{10} + x^{7} + 1$                    | 1023               |

| 11   | $x^{11} + x^{9} + 1$                    | 2047               |

| 12   | $x^{12} + x^{11} + x^{10} + x^{4} + 1$  | 4095               |

| 13   | $x^{13} + x^{12} + x^{11} + x^{8} + 1$  | 8191               |

| 14   | $x^{14} + x^{13} + x^{12} + x^{2} + 1$  | 16383              |

| 15   | $x^{15} + x^{14} + 1$                   | 32767              |

| 16   | $x^{16} + x^{14} + x^{13} + x^{11} + 1$ | 65535              |

| 17   | $x^{17} + x^{14} + 1$                   | 131071             |

| 18   | $x^{18} + x^{11} + 1$                   | 262143             |

| 19   | $x^{19} + x^{18} + x^{17} + x^{14} + 1$ | 524287             |

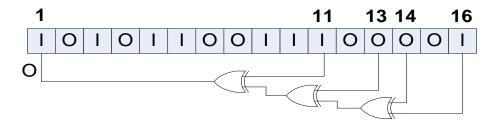

To build a digital jitter, a Linear Feedback Shift Registers (LFSR) can be utilized as a Pseudo Noise Generator [3]. Linear Feedback Shift Register is a shift register that generates pseudo-random sequences. It consists of generating a new input bit by applying a linear function to some of the previous states called taps. There are only two linear functions: *xor* and *inverse-xor*. In LFSR the former one is commonly used. The initial state of LFSR is called seed. Seed is a sequence of bits in registers after a reset of a system. Because LFSR is deterministic, it is possible to determine the next and the previous state from the current set of bits. Therefore, it is recommended to use different seeds for jitter generator in order to avoid the same jitter size in each cycle. Moreover, the seed with all 0s is forbidden because the *xor* function would never generate

any other state then. It is possible to create both hardware and software versions of the LFSR.

The period of the LFSR depends on the number of bits it contains. It can be determined from the equation:  $2^n - 1$ , where n is a length of LFSR. LFSR feedback can depend on two or more taps as it is presented in table 2.1. There are two types of LFSR:

Fibonacci LFSR – a new input bit is created by at least two taps. Signals from that taps are XORed and the value is placed in front of the shifter (Figure 2.15).

The last bit disappears and all other bits are shifted to the right.

**Figure 2.15.** 16-bit Fibonacci LFSR. The feedback tap numbers correspond to a primitive polynomial in table 2.1. Hence, the register's maximum period equals to **65535** states excluding the all-zeroes state which is forbidden

Figure 2.16. 16-bit Galois LFSR. The register numbers correspond to the same primitive polynomial as the Fibonacci instance in table 2.1. but are presented in reverse to the shifting direction. Here also the register's maximum period equals to 65535 states excluding the all-zeroes state which is forbidden

• Comparing to Fibonacci LFSR, in Galois LFSRs the taps are XORed with the output bit before they are placed in the next register (Figure 2.16). In particular, when an output bit is equal to "0", then all taps preserve their values. The register is only shifted to the right and the output bit "0" becomes a new input bit. On the other hand, when the output bit is "1", then all taps change their value

and the register is shifted to the right. The new input bit is "1". Galois LFSR does not calculate each tap in order to produce a new input bit. Thus, it is faster and calculations can be processed in parallel reducing the propagation time.

The Galois LFSR is commonly used in digital circuits. However, for conducting research and simulations it does not matter which solution is chosen.

Figure 2.17. Sample jitter generator schema

In order to create a programmable Delay Element (DE) a chain of invertors or buffers can be utilized [12]. The whole solution for a reasonable jitter generator is presented in Figure 2.17. It consists of:

- Clock generator (input clock signal)

- Chain of delay elements (each contains two invertors)

- Multiplexer

- 4 bit LFSR

The aim of a multiplexer is to select an appropriate delay line that will be propagated to the output (CLKOUT). The LFSR is triggered by the last additionally delayed clock signal (CLKDLY) to avoid any metastability and glitches that could occur at the output of jitter. However, in order to speed up simulations and prevent recalculations of Delay Elements, a jitter generator available in the GALS EMI simulator was applied. It had no adverse effect on the final results.

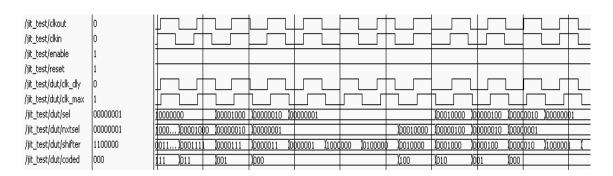

Figure 2.18. Behavioral simulation of a jitter generator

An outlook of a behavioral simulation of the jitter generator described before is presented in Figure 2.18. *Clk\_max* (corresponding to CLKDLY signal in Figure 2.17) is a signal that triggers the LFSR. This signal has a maximum delay in order to prevent glitches occurring. Moreover, the LFSR is triggered when all the clock signal (input and output) are in the low state. Thus, there is enough time for registers to complete proper setup. The *Sel* signal represents a value of LFSR. Although it contains 4 bits, only 3 are used (the *coded* signal) in order to select 1 out of 8 delay lines that is propagated to the output. It can be clearly observed, that during each cycle, the delay of output clock is propagated according to the selected delay element.

In GALS systems with pausable clock only a jitter can be added to a system (to each GALS module). Integrating a phase shift would be a useless procedure. Phase shift is already present by the nature of the GALS methodology.

Table 2.2 presents the results of measurements of pseudo-random jitter generator at RTL level (register transfer level). They were determined by simulation, in order to obtain an accurate data about jitter to investigate its impact on the performance of the entire digital system [53]. The input clock was set at 100 MHz (10 ns cycle time). "Delay Line" means a line that has been selected in current cycle. In addition, individual

parameters were determined for each of the lines. The second column presents the delay between the transition of the input clock and the output from low to high state. Despite the fact that the delay is increased with the increase of the delay line, it is not linear. The difference between the two values is not constant and it is caused by various path lengths that go to multiplexer. However, it is assumed for further research, the average rate as 130 ps and it is equal to the propagation time of two connected inverters.

**Table 2.2.** Jitter generator – output signal delay

|       | Delay Line | Delay (ps) |

|-------|------------|------------|

| MIN   | 0000001    | 207        |

|       | 00000010   | 357        |

|       | 00000100   | 479        |

| delay | 00001000   | 635        |

|       | 00010000   | 751        |

|       | 00100000   | 906        |

|       | 01000000   | 1019       |

| MAX   | 10000000   | 1175       |

It can be observed (Table 2.2) that using 100 MHz clock and 8-elements delay line, the maximum clock cycle reduction is 10%. This value is more than sufficient for our study, because in practice and in the literature there are no examples of a successful implementation of a synchronous system with higher jitter parameters. On the other hand, if 200 MHz clock source is used and 4 delay elements are applied, a 10% jitter is also created. The results would be similar with a slower clock source. Using a 50 MHz clock could increase the resolution of the generated fluctuations with the same delay elements (inverters) precision. It is also possible to replace the delay elements implemented as two connected inverters by using dedicated components (e.g. specially elongated tracks). It is assumed that the delay generated by such a construction would have shorter propagation time than two inverters in that technology. This would increase the resolution of jitter and its further ability to generate appropriate fluctuations at higher clock speeds.

### 2.4. GALS practical example in reducing EMI

In papers [22] and [23] a case study of implementing GALS technology in order to reduce EMI has been analyzed and presented. The work is based on a simulator described in this dissertation and developed by the author. GalsEmilator facilitated a process of selecting appropriate parameters of GALS system in order to maximize EMI reduction in such a circuit.

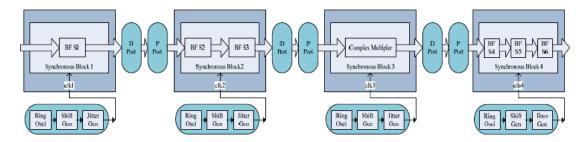

The investigated circuit consisted of 64-point GALS FFT processor divided into two cascaded 8-point FFT algorithms (Figure 2.19). The 8-point FFT was build with a novel Radix-23 FFT algorithm, which utilizes 3 stages of the butterfly (BF) structure. In that case and architecture, there was only one special twiddle factor multiplier necessary to build a pipelined 64-point FFT.

Figure 2.19. Block diagram of the GALS FFT processor [22]

As it is described in the paper [22], the authors designed the pausable clocking based GALS architecture (Figure 2.19) in order to reduce EMI (that is crucial for analog/digital circuits design) caused by simultaneous switching noise (SSN). It was necessary to develop special GALS connections between each block in order to support communication and data flow. For that reason, each synchronous block (there are 4 of them) is covered with an asynchronous wrapper. The asynchronous wrapper contains local clock generator and at least one asynchronous port (the middle blocks contain both I/O ports). Furthermore, each clock generator can be modulated. It was expected that such a modification of a regular chip design should reduce sharp peaks in the system supply current and finally the EMI of the whole system.

The 64-point FFT circuit was divided into seven functional sub-blocks in the pipelined processor. There are six butterfly structures and a complex multiplier. The sub-blocks have been arranged into four synchronous blocks according to their power

and current requirements. In order to establish the power consumption precisely, the authors prepared dynamic power analysis using simulation waveforms of the synthesized netlist in the IHP  $0.13\mu m$  CMOS standard cells library technology. Table 2.3 shows the results of arranging the sub-blocks of the GALS FFT chip into four synchronous blocks. The blocks have similar power and current consumption.

**Table 2.3.** GALS FFT circuit partition according to power and current consumption [22]

|                 | Sync. Block 1 | Sync. Block 2 | Sync. Block 3 | Sync. Block 4  |

|-----------------|---------------|---------------|---------------|----------------|

| Function        | BF Stage 1    | BF Stage 2/3  | Complex Mult. | BF Stage 4/5/6 |

| Area (1)        | 38556μm²      | 46119 μm²     | 47459 μm²     | 40547 μm²      |

| Number of FF    | 651           | 637           | 173           | 362            |

| Average power   | 1.2mW         | 1.5mW         | 1.2mW         | 1.7mW          |

| Average current | 1mA           | 1.25mA        | 1mA           | 1.4mA          |

Note: (1) Reported by Synopsys DesignCompiler;

(2) Reported by Synopsys PrimeTime at 80MHz working frequency.

In this work, two techniques were applied to the pausable local clock generators in order to modify the clocks of each synchronous sub-block: phase modulation and frequency modulation.

**Figure 2.20.** Current profiles of four synchronous GALS FFT blocks with phase modulation [22]

**Phase Modulation** – local clock generators' signals are first propagated through a programmable delay line. Therefore, the rising edge of each synchronous block's clock can be shifted independently. This modification leads to diversification in time of synchronous blocks' switching activities. Moreover, it allowed reducing sharp peaks of

the whole system supply current by spreading them over the whole period. In that research the clock signals of each synchronous block has been shifted evenly among clock period. These parameters are presented in Table 2.4. The results of such a modification are shown on a simulation in Figure 2.20 where a phase shift has been applied to each synchronous GALS block.

**Table 2.4.** Phase modulation of each clock generator among synchronous blocks [22]

|                    | Sync. Block 1 | Sync. Block 2       | Sync. Block 3       | Sync. Block 4        |

|--------------------|---------------|---------------------|---------------------|----------------------|

| t <sub>CLK</sub> + | 0             | T <sub>CLK</sub> /4 | T <sub>CLK</sub> /2 | 3T <sub>CLK</sub> /4 |

This technique is also applied to traditional synchronous designs as it was stated before, in order to spread switching activities of the processor. It allows designers to modify a shape of current supply in digital circuits. They can adjust both clock latency as well as clock skew in the global clock tree network. However, this modification is restricted by a synchronous design where limits are applied to setup-time and hold-time of the circuit. Therefore, only up to several percent of clock period the clock phase modulation can change. On the other hand, there is GALS design where asynchronous ports let the whole system to work with independent clocking systems. Thus, the parts of the system can work with a clock shifted even 50% of the base clock period. GALS technology enable digital circuit designers to overcome limits imposed by a synchronous design and apply phase shift to each GALS block without restrictions.

Frequency modulation – jittered clock signal; the second approach to minimize EMI and reduce SSN is to introduce a quick frequency modulation – clock jitter. It spreads the supply current in spectrum. The authors of the GALS FFT system added that feature to their design. Figure 2.21 and 2.22 present a jitter generator model and its clock period variations. The input clock signal is propagated through a delay line which is built of a chain of delay elements. The output signal delay depends on the line selected by a multiplexer. There are various ways to control the multiplexer and thus generating delayed signal. It can be either liner or randomized in terms of selecting delay and further modulation of the input signal. In both cases designers should focus

their attention on avoiding glitches on the output clock, which could have a detrimental effect on whole GALS system.

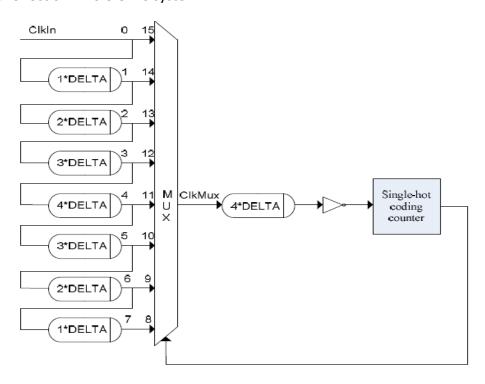

Figure 2.21. Jitter generator schema in GALS FFT digital circuit [22]

Figure 2.22. Triangular modulation of clock frequency in GALS FFT digital circuit [22]

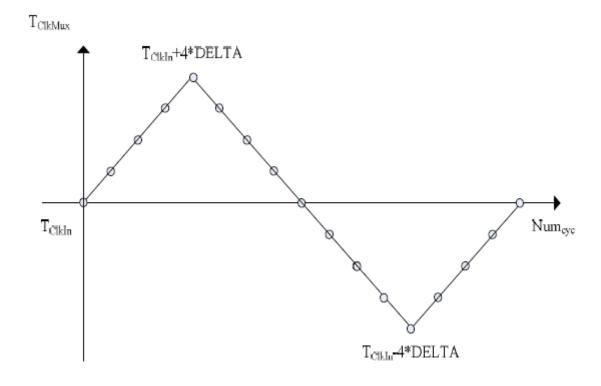

The authors of the GALS FFT systems have utilized a single-hot coding to modulate the output clock in a linear mode. In that case, the clock period  $T_{CLK}$  alters from  $T_{CLK}$ -4DELTA up to  $T_{CLK}$ +4DELTA, where DELTA determines modulating granularity and is equal to 0,15ns. Moreover, the four local clocks are initialized with different offsets on  $T_{CLK}$  in order to improve randomization of the whole system clocks' signals.

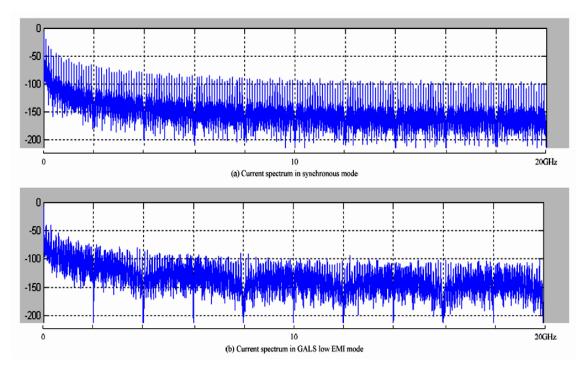

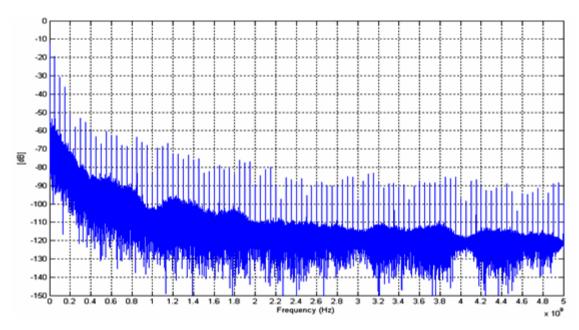

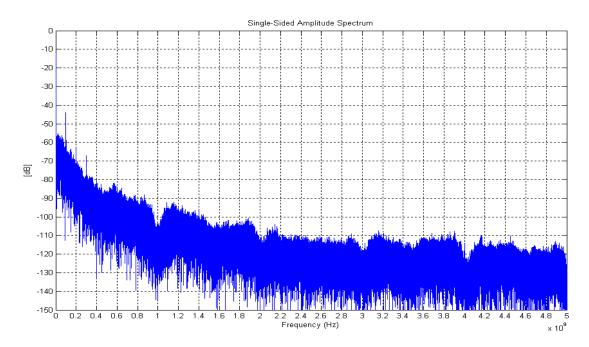

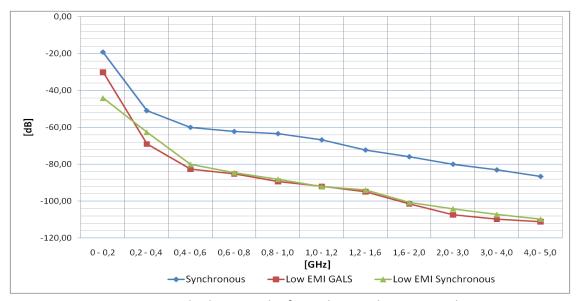

In order to verify the designed GALS FFT system and compare its parameters regarding EMI/SSN with its synchronous counterpart, a GalsEmilator has been utilized. Details about system fragmentation, clock frequencies and their modulations of each block, maximal current requirements of each synchronous block were used in the program to generate current profiles of the systems. Afterwards, a current supply spectrum of both systems has been compared in a range from 0 to 20GHz (Figure 2.23). It is clear that the attenuation in GALS design averages around 10 dB in frequency domain comparing to the synchronous approach. It allowed the assumption that by utilizing clock modulation and system portioning, SSN can be reduced significantly and thus EMI in the digital circuit. Further investigations confirmed that the simulations results are true in terms of real chip testing.

**Figure 2.23.** Comparison of current spectrum of synchronous mode and GALS low-EMI mode with MATLAB simulation in GalsEmilator

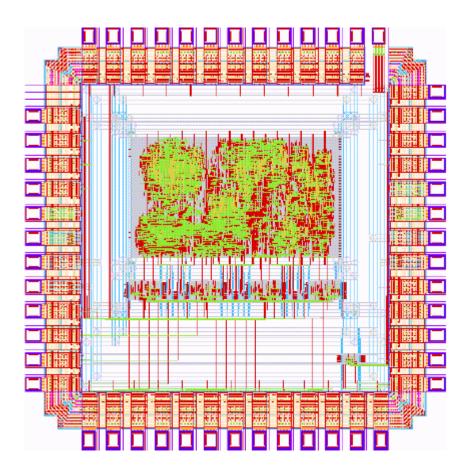

The described 64-point FFT processor was fabricated in the IHP (Institute for High Performance Microelectronics, Frankfurt, Oder).  $0.13\mu\text{m}-1.2\nu$  six fold-metal standard CMOS technology [22]. The die size is  $1730~\mu\text{m}$  x  $1730~\mu\text{m}$  with 52 IO pads, as it is presented in Figure 2.24. Next, the chip was placed in a 64-pin PQFP, and the final product was successfully tested and measured in terms of its electric and EMI characteristic in IHP.

Figure 2.24. Die micrograph of the tested GALS FFT processor [22]

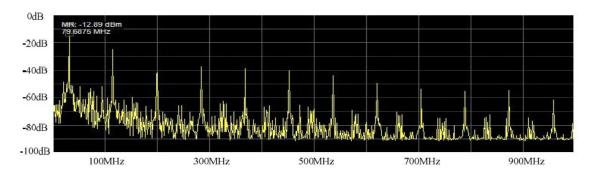

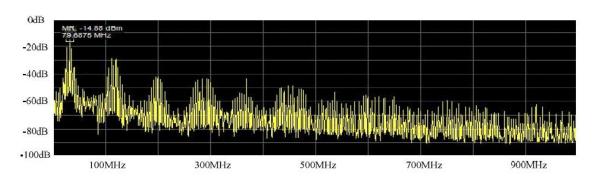

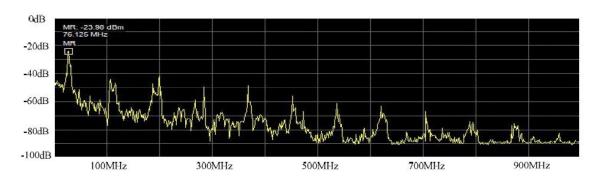

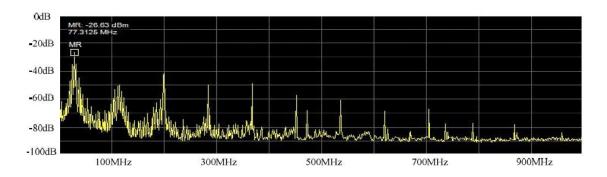

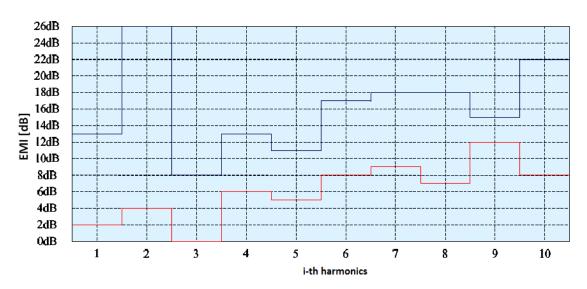

The supply voltage ( $V_{dd}$ ) of the produced chip has been measured in frequency domain against different working modes. The results are presented in Figures 2.25, 2.26, 2.27, 2.28. Moreover, the corresponding attenuation of the spectral peaks has been shown in Figure 2.29.

Figure 2.25.  $V_{dd}$  spectral analysis of the produced GALS FFT working in Synchronous mode [22]

Figure 2.26.  $V_{dd}$  spectral analysis of the produced GALS FFT working in Synchronous mode with clock jitter [22]

Figure 2.27. V<sub>dd</sub> spectral analysis of the produced GALS FFT working in GALS mode [22]

**Figure 2.28.** V<sub>dd</sub> spectral analysis of the produced GALS FFT working in GALS mode with clock jitter [22]

Figure 2.29. EMI reduction in the spectral peaks of i-th harmonics in the tested GALS FFT system. Red line – synchronous mode with jittered clock; Blue line:

GALS mode with jittered clock [22]

The results confirmed that presented further in this dissertation simulator is fully functional. It can be seen from the Figure 2.29 that even a relatively simple GALS system reduces EMI significantly in comparison to its synchronous counterpart (11dB of the main peak). Moreover, according to simulations and real-life tests, jitter added to a clock generator reduces EMI further, mainly among higher harmonics. This confirms a significant match between simulations of the model and actual chip behavior. Simulated gain was around 10,5 – 11 dB and the measured one was equal to 11dB. The model was run with a limited data, where usually an approximate shape of a current in every

block is necessary to achieve better results. However, even without the data, calculations showed were an adequate prediction.

# 3. Modeling EMI in digital systems

In this chapter, GALS EMI simulator and GALS modeling approach with hybrid algorithm are presented. First, the developed software tool is described in details. Next, several GALS topologies are explained. Additionally, three different data transfer scenarios are demonstrated in GALS systems. Finally, system's parameters utilized for simulations and hybrid optimization are explained briefly.

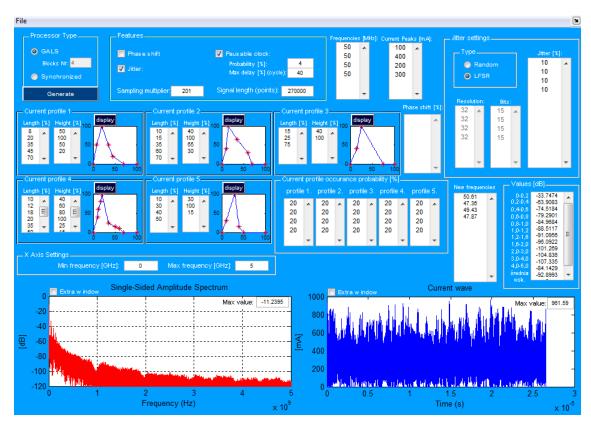

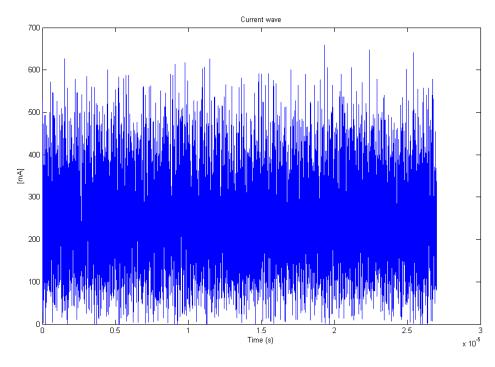

## 3.1. GALS EMI simulator

In order to investigate EMI characteristic in the digital circuits caused by the digital clock behavior, a dedicated software tool called "GalsEmilator" has been developed. GalsEmilator (Figure 3.1) is a program created in Matlab in order to investigate EMI in various types and topologies of GALS systems (including synchronous solutions). It contains a number of options to model, as precisely as possible, the parameters of each GALS/synchronous system. Hence, it is feasible to observe the noise behavior in frequency and time domain simultaneously.

Figure 3.1. GalsEmilator – software to model EMI in synchronous and GALS systems

In the developed tool, main focus was to enable modeling different current shapes for different clock cycles. The software allows describing up to five different current profiles and specifying the probability of their appearance in the system.

For each block of the synchronous system, a clock phase shift (in respect to the global clock frequency) and additional jitter can be also set. For GALS modules, we can model extra clock jitter and also model pausable clocking [8] as a dominant technique for low-EMI GALS circuits. A model of GALS with pausable clocking allows us to simulate GALS wrappers that can pause the clock in order to perform a handshake operation. This behavior can be modeled by setting a probability of pause occurrence and a maximum delay of the pause. The delay is variable and, therefore, in our model it is randomized.

All simulated results, as shown in Figure 3.1, can be observed and analyzed both graphically and in generated tables. The complete software has its own user-friendly GUI.

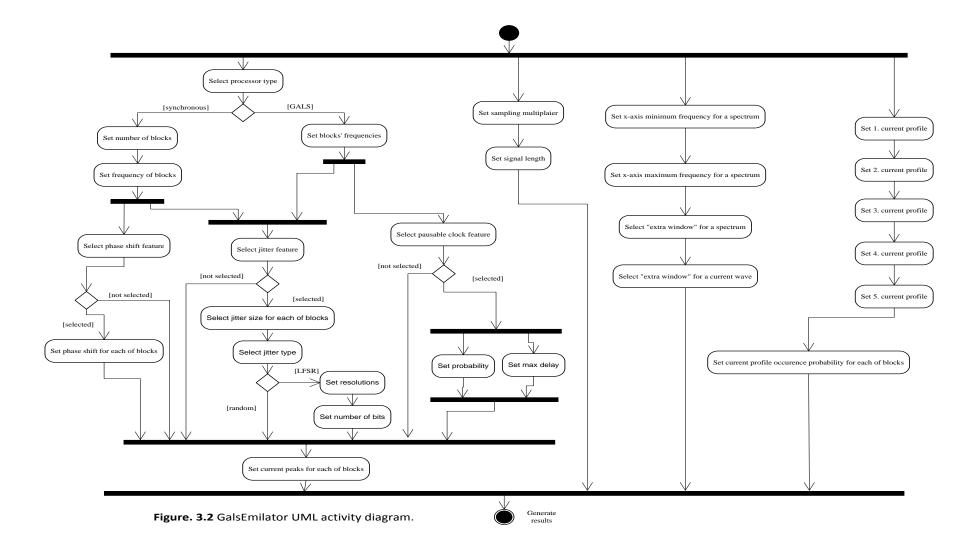

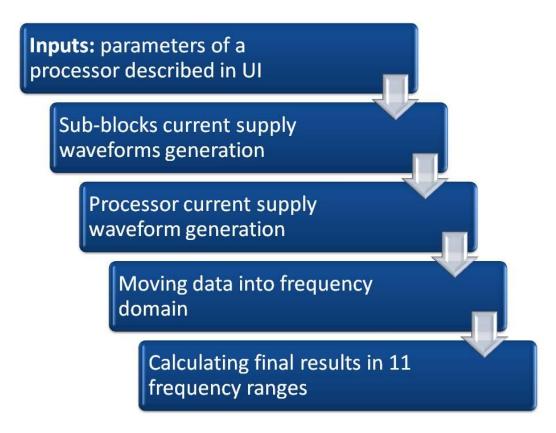

#### 3.1.1. Simulator description

Figure 3.2 presents an UML activity diagram for GalsEmilator. It shows the way in which the software should be handled properly. All actions to run a successful simulation are presented step by step. The simplified model of GalsEmilator algorithm is presented in Figure 3.3.

First of all, it is possible to select, in the simulator GUI, a chip type. There are two previously described designs: GALS or Synchronous approach. After selecting a synchronous system it is impossible to select several options that are intended for GALS system e.g. "pausable clock". Moreover, in GALS system, each sub block's frequency have to be specified, whereas in synchronous system only one is necessary.

Up to five current profiles can be described in the GUI by specifying their shapes in percentage. Hence, every current shape will be recalculated according to block's frequency and sampling frequency creating a matrix of values for every block. Moreover, it is necessary to specify current shape occurrence probability for each of the blocks. The values determine how many times per 100 cycles every shape is going to occur. Usually, the equally distributed numbers are placed as it is difficult to define real figures within testing environment.

Figure 3.3. Simplified model description of GalsEmilator algorithm

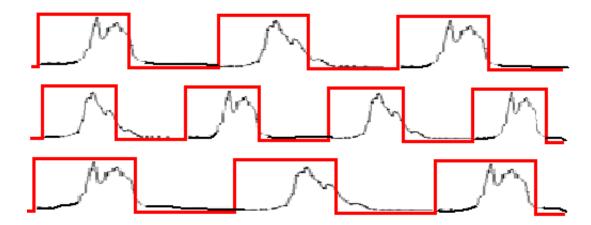

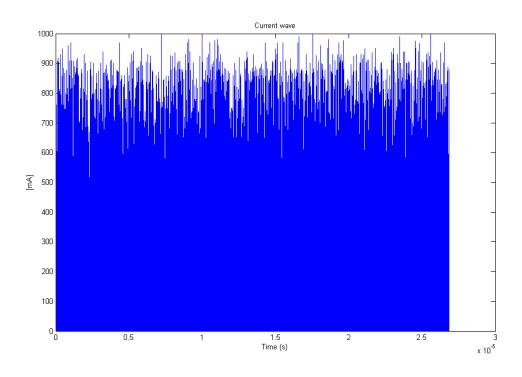

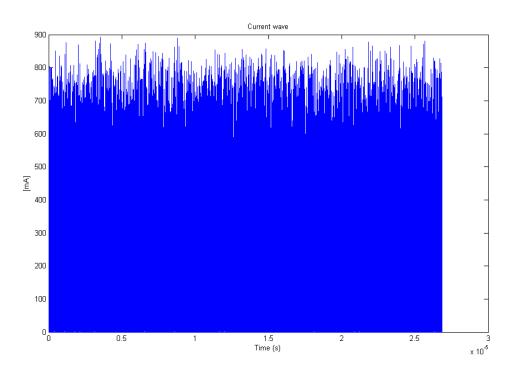

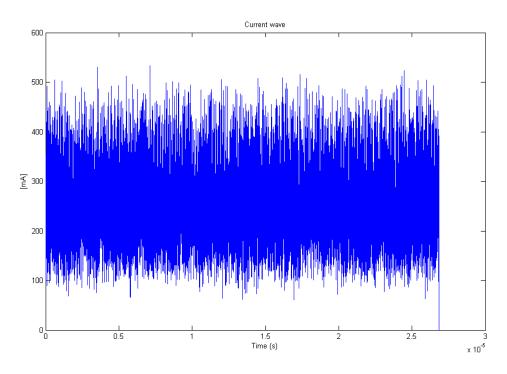

Next, current waves for sub blocks are calculated in a time domain according to the blocks' frequencies, current profiles and their probability. Hence, the current waves are composed with a number of single patterns (Figure 3.4).

**Figure 3.4.** Sample clocking signals (red color) and corresponding current waves of GALS sub blocks. The simulator generates such waveforms in order to calculate a final wave composed of these sub-waveforms

At that moment there is one wave per block. Each wave can be additionally modified according to the features described later. Further, all waves are summed into one final wave of a whole chip. The FFT (Fast Fourier Transform) is used in order to move the final wave from the time domain into the frequency domain. After the transformation, it is possible to observe the whole spectrum and the EMI reduction in several ranges of frequency:

- 0,0 0,2 GHz (without 0,0)

- 0,2 0,4 GHz

- 0,4 0,6 GHz

- 0,6 0,8 GHz

- 0,8 1,0 GHz

- 1,0 1,2 GHz

- 1,2 1,6 GHz

- 1,6 2,0 GHz

- 2,0 3,0 GHz

- 3,0 4,0 GHz

- 4,0 5,0 GHz

The ranges were set according to the basic research frequency at 50 MHz and power corresponding to each of range. The higher range, the lower power it contains, so the range is wider. The ranges of spectrum in the lower frequencies are shorter because the values change more rapidly. On the other hand, in the higher frequencies the spectrum is flatter. Thus, the ranges can be relatively wider. Moreover, the ranges were set according to a case study (described before GALS FFT) that was investigated. The ranges can be easily scalable for different basic frequencies.

The result is only one value per range which indicates the highest value in the range (the noisiest frequency which is usually the i-th harmonics). The values (power) of a spectrum are presented in dB regarding the total current supply indicated as current peaks per each sub block, where A is an amplitude of i-th frequency (according to sampling frequency) in the spectrum,  $A_0$  is total current supply (1A in this research):

$$L_{dB} = 10log_{10} \left( \frac{A^2}{A_0^2} \right) = 20log_{10} \left( \frac{A}{A_0} \right)$$

(3.1)

The second set of options that influences the way a waveform looks in each sub block are "Features". It is possible to set:

- clock phase shift of each sub block (useful only with a synchronous design)

- jitter

- pausable clock (possible only for GALS systems)

- sampling multiplier

- signal length

Clock phase shift option contains additional text input box, where each shift of a block is defined in percentage. This feature moves a wave in time according to an indicated fraction (percentage) of its period. It can be useful when a mesochronous [40] system is investigated regarding EMI.

Jitter introduces a phase modulation (rapid phase fluctuations) to a waveform. It modifies slightly, up to the defined part of a period, the starting point of a rising edge, while the time of high level stays constant. Hence, jitter can increase or decrease frequency for one cycle but generally the base frequency remains unchanged. With the simulator GUI it is possible to select between random jitter, that uses the Matlab embedded random number generators (with the period of (2^19937-1)/2) and LFSR (Linear Feedback Shift Register). Selecting the LFSR method is necessary to specify also the LFSR length and the resolution of the delay chain. The LFSR length determines a number of bits used to create LFSR, thus the length of the period of a jitter is defined. The resolution of delay chain describes how many possible states of jitter will be applicable for an input clock signal.

Pausable clock option allows simulation of GALS wrappers that can stop a clock in order to confirm the handshake operation. It is necessary to specify occurrence probability of a pause and a maximum delay (fraction of a cycle). The delay length can vary in each step because it is randomized. The length that is specified indicates only the worst case scenario.

The two last options are focused indirectly on the whole final wave. Sampling multiplier describes how much faster would be the sampling frequency in comparison with the highest frequency of the blocks. It is suggested to remember that the lowest possible sampling frequency is twice the highest measured waves' frequency (Nyquist–Shannon sampling theory). However, usage of the lowest sampling frequency is not

recommended because each cycle of the fastest sub block would be modeled only with 2 points. The suggested sampling multiplier is 200, although 100 would be also enough. The latter one is sufficient because the current shape of the fastest module will be modeled with 100 points which is usually enough to present every detail. However, the higher sampling multiplier the more adequate model but also the longer time of computations. The difference in results between those two sampling multipliers was insignificant but not every case had been investigated. Also the signal length that describes how long the modeled signal will be in points can be set.

It should be pointed out that each point of a waveform is calculated according to the sampling frequency. Generally, if there would appear a significant difference between two simulations, the signal length should be extended. It ought to reduce the variations between simulations with the same settings caused by several random values e.g. pausable clock or jitter generated by the Matlab random method. If the sampling frequency is too low, it might also be necessary to increase its value in order to improve results.

At the bottom of the GUI two small graphs are present. Although they are embedded into a GUI, there are extra options (checkboxes) that allow user creating the separate flexible charts. Then, all parameters of a chart can be modified. The latter graph shows a current wave in the time domain. The former displays the same wave in a frequency domain after Fast Fourier Transform. The values presented in the chart are compared with the sum of current peaks and presented in dB. Additionally, it is possible to specify the range of frequencies that will be displayed in a chart in order to investigate a fixed area. It facilitates the signals comparison and further evaluation.

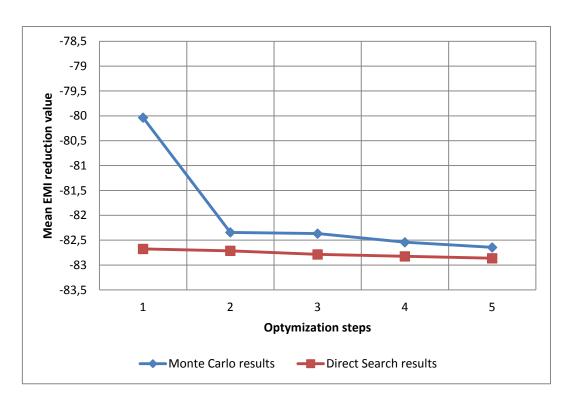

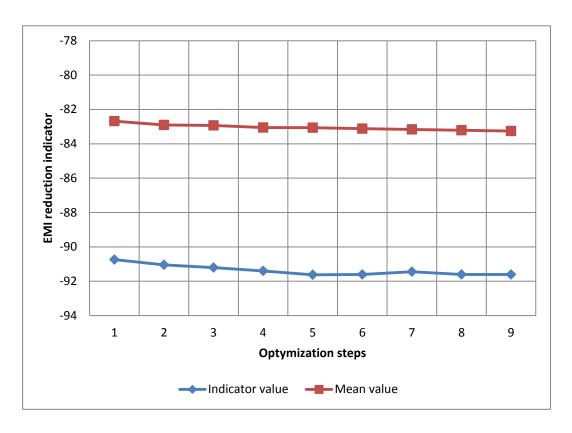

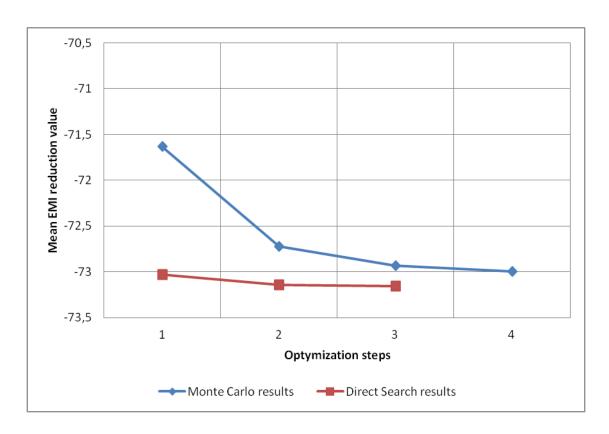

# 3.2. Hybrid optimization algorithm

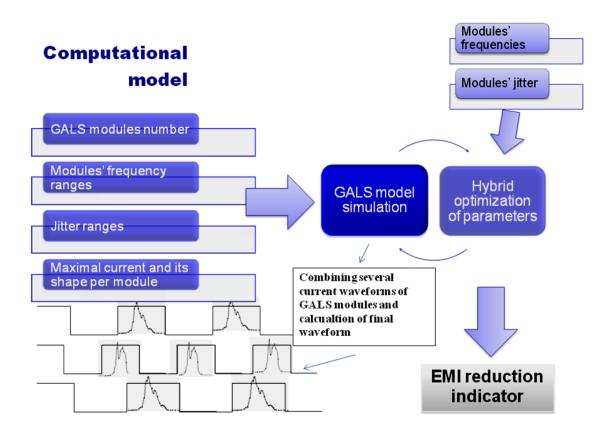

In order to investigate closely an influence of frequencies set against EMI reduction in GALS systems, it was necessary to design a hybrid optimization algorithm. The whole process is presented in Figure 3.5. Initial studies have been conducted which proved that the regular optimization algorithms are insufficient to give satisfactory results. It is because of the number of dimensions, which increase with the number of GALS modules, and irregular shape of the objective function with large number of local minimums. Therefore, a hybrid optimization shell was added to the GalsEmilator (Fig-

ure 3.5). The computational schema presented in the picture shows that there is a necessary number of GALS modules in the mode, modules' frequency ranges, jitter ranges or constant values, maximal current and its shape per GALS module to begin searching algorithm. As it was described before, the simulator calculates the results with initial parameters. Then, the parameters are changed according to hybrid optimization algorithm.

**Figure 3.5.** Computational model of hybrid optimization regarding EMI reduction in GALS systems

The objective function F is programmable, thus it can be either an average reduction of all ranges of investigated frequencies (there are used 11 range of frequencies from 0 to 5Ghz) or a special indicator where each reduction in a range has a rate (sum of rates is equal to 1):

$$F = 0,15r_1 + 0,14r_2 + 0,12r_3 + 0,11r_4 + 0,08r_5 + 0,08r_6 +$$

$$+ 0,07r_7 + 0,07r_8 + 0,06r_9 + 0,06r_{10} + 0,06r_{11}$$

$$(3.2)$$

where  $r_i$  is maximal noise of EMI in each of 11 ranges described before. Corresponding numbers are factors of each of the ranges. The aim of hybrid optimization is to achieve a maximal reduction of EMI, it means  $F \rightarrow \min$ .

The objective function F should be chosen according to requirements and problem specification. For example when there is a need to attenuate EMI in low frequencies the factors can be set to focus only on that range and making the other ones obsolete. In this dissertation the average method has been utilized, however the presented indicator is also shown in results in order to illustrate the differences.

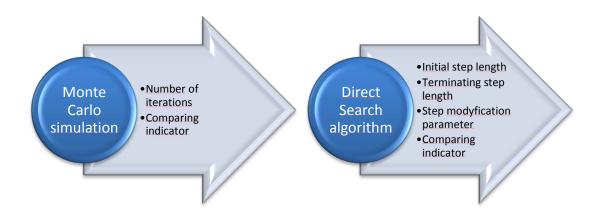

During optimization process two sequentially programmed algorithms are used (Figure 3.6). First of all, the Monte Carlo simulation is required to find the best global solution because there are many local minimums. According to the number of iterations and initial precision the algorithm runs in a loop.

Figure 3.6. Hybrid optimization components and its parameters

When the Monte Carlo stage is finished, the best result is propagated to a second optimization algorithm — direct search algorithm (simple modification of Rosenbrock' method). It is powerful enough, no-gradient and relatively fast algorithm to improve the solution. It consists of searching better results among orthogonal vectors in a n-dimensional space according to number of GALS modules. The orthogonal

set of vectors is created according to rule where two vectors x and y are described in a unitary space X with scalar product  $\{\cdot,\cdot\}$ , where  $\{x,y\}=0$ . The search can be also completed in an opposite direction to the orthogonal set. The initial step length is decreased when there are no better results until described value. A better result is checked among the set of vectors in every iteration. When it is found, the current point is moved to the best one in next step and the whole procedure is repeated. When there is no better solution, the step length is corrected accordingly to programmed value and the procedure is restarted. When the shortening of a step-length does not bring a better value and the step length is less than the required precision, the algorithm stops.

## 3.3. GALS modeling

The software was used to model and investigate EMI characteristics in different GALS and synchronous systems. For the GALS system, the focus was on the pausable clocking scheme that is very often used in contemporary GALS NoC systems [8], [9]. In order to accurately model the clock waveform of the GALS system, all evaluated systems have been described in VHDL and simulated. Next, the clock behavior is automatically extracted from the simulation conducted in ModelSim using the developed software tool. The second version of software was designed in order to facilitate this feature. Data is directly moved to the EMI simulator and evaluated. Such appendage of the software was needed to support exact matching to the real system behavior of the GALS interfaces. It was particularly challenging to extract clock behavior during the handshake process between the GALS blocks when clocks are paused, without access to real simulation data.

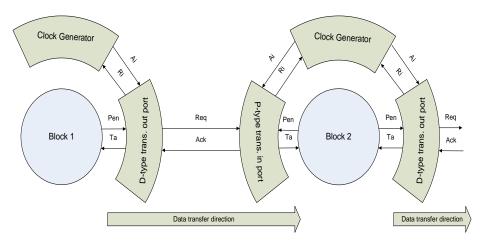

Figure 3.7. Sample of connection between two adjacent LS blocks used in models

In the VHDL (Very High Speed Integrated Circuits Hardware Description Language) models, the D-type output and P-type input GALS ports [7] have been used as shown in Figure 3.7. 'Demand Type' (D-type) ports pause the clock immediately after receiving request from the Locally Synchronous (LS) block. For the input side, 'Poll Type' (P-type) ports have been used. The standard 4-phase handshake operation between adjacent GALS modules was entirely modeled in the simulation.

## 3.3.1. Topologies of the evaluated GALS systems

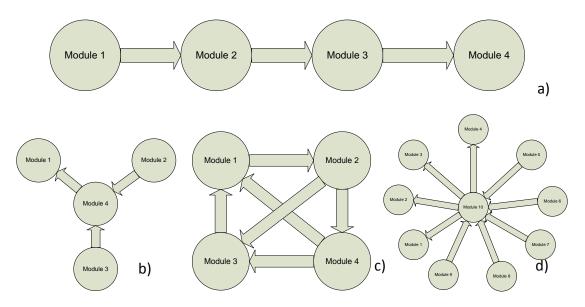

Figure 3.8. Various topologies of models: a) point-to-point b) star c) mesh d) large star

In evaluation four different structures of GALS circuits have been analyzed as shown in Figure 3.8. Different system topologies [38] have been investigated. Here, point-to-point (a), star (b) and mesh (c) topologies were taken into consideration. In order to check whether a granulation can influence the reduction of EMI, the star with a higher number of blocks (d) has been also examined. The goal was to evaluate different interconnect structures and to verify their impact on EMI in GALS systems. The arrow in Figure 3.8 indicates a direction of handshake and data transfer. In a point-to-point topology the direction is obvious. The modules have to be combined in a straight line where each module is connected with another one. In other topologies the direction of data transfer is rather unrestricted.

#### 3.3.2 Data transfer scenarios

The outlook of the clock waveform varies significantly between different intensity of the data transfer since the clock pausing occurs only during the handshake process. For that reason, three different scenarios of the system behavior have been modeled:

- A. Low data transfer, where the data transfer is performed relatively rarely (for instance, once per 6 clocks).

- B. Medium-to-high data transfer, where half of the clock cycles are involved in data transfer.

- C. Burst mode, where more than 80% of the clock cycles are data-transfer related.

**Table 3.1.** Patterns for low data transfer (A) for each designed topology

|           | 4-module point-to-point, star | 4-module mesh | 10-module star |

|-----------|-------------------------------|---------------|----------------|

| Pattern 1 | 100000                        | 100000        | 100000         |

| Pattern 2 | 000100                        | 000010        | 000001         |

| Pattern 3 | 000001                        | 001000        | 001000         |

| Pattern 4 |                               | 000001        | 010000         |

| Pattern 5 |                               | 010000        | 000010         |

| Pattern 6 |                               | 000100        | 001000         |

| Pattern 7 |                               |               | 001000         |

| Pattern 8 |                               |               | 100000         |

| Pattern 9 |                               |               | 000100         |

**Table 3.2.** Patterns for medium data transfer (B) for each designed topology

|           | 4-module point-to-point, star | 4-module mesh | 10-module star |

|-----------|-------------------------------|---------------|----------------|

| Pattern 1 | 110100                        | 010101        | 101010         |

| Pattern 2 | 101010                        | 111000        | 111000         |

| Pattern 3 | 001110                        | 001101        | 101100         |

| Pattern 4 |                               | 101100        | 001011         |

| Pattern 5 |                               | 000111        | 101010         |

| Pattern 6 |                               | 011100        | 000111         |

| Pattern 7 |                               |               | 100011         |

| Pattern 8 |                               |               | 101001         |

| Pattern 9 |                               |               | 011100         |

Table 3.3. Patterns for burst data transfer (C) for each designed topology

|           | 4-module point-to-point, star | 4-module mesh | 10-module star |

|-----------|-------------------------------|---------------|----------------|

| Pattern 1 | 110111                        | 111011        | 011111         |

| Pattern 2 | 011111                        | 011111        | 111011         |

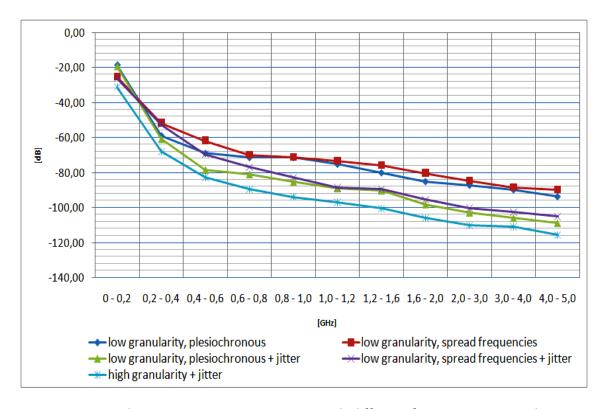

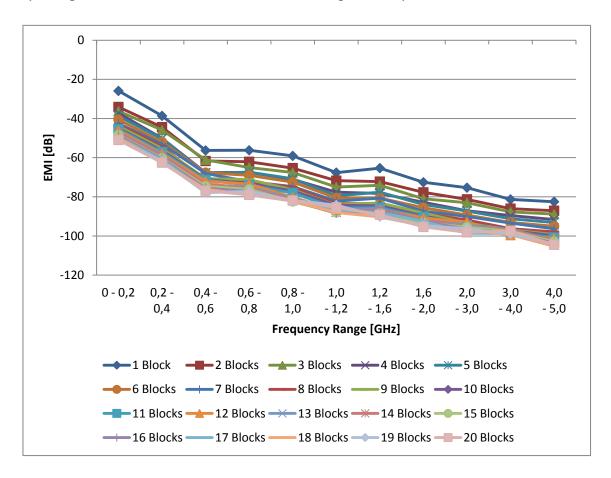

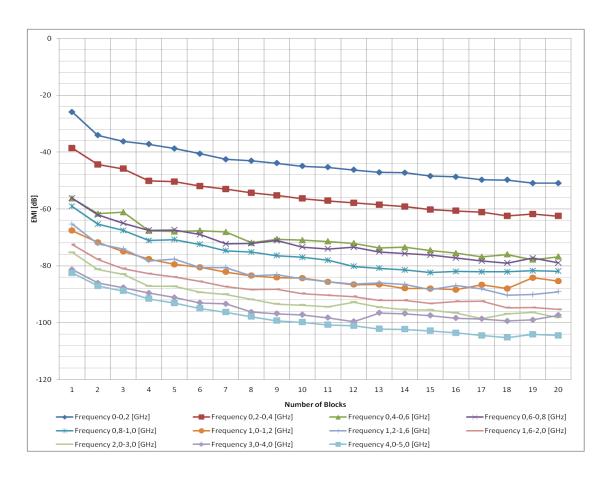

| Pattern 3 | 111101                        | 110111        | 111110         |